Clock de 25MHz com FPGA

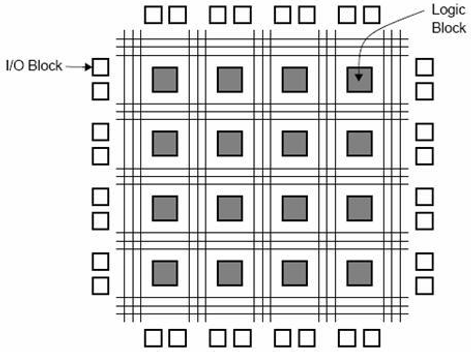

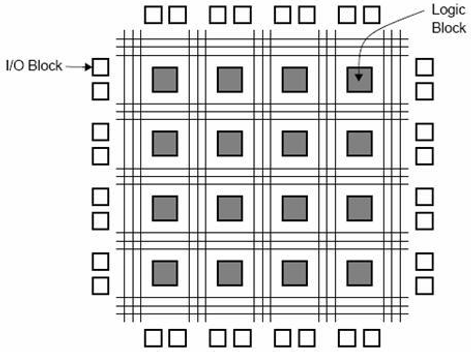

Os FPGAs (Field-Programmable Gate Array) são dispositivos que nos permitem aplicações e recursos avançados na Eletrônica, largamente utilizados em instrumentação (como osciloscópios digitais e geradores arbitrários), pelo fato de sintetizarem o hardware que queremos implementar na prática. Ao contrário dos processadores, os FPGAs apresentam a solução em um hardware sintetizado por suas matrizes internas (Figura 1).

No presente artigo, propomos uma aplicação que irá auxiliar o leitor no desenvolvimento de projetos que necessitam de bases de tempo precisas com FPGAs. Aproveitando da vantagem do dispositivo em trabalhar com altas frequências (daí a larga aplicabilidade em instrumentação e telecomunicações), vamos descrever o hardware para gerar um sinal de clock de 25MHz, com um FPGA da família Cyclone IV da fabricante Altera. Quando falamos em código para FPGA, não podemos nos referir como uma linguagem de programação e sim, como uma linguagem de descrição de hardware. As linguagens de descrição de hardware (HDL’s – hardware description language) mais utilizadas na indústria são a Verilog e a VHDL.

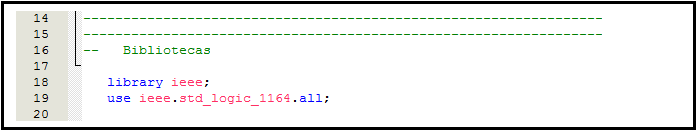

Para sintetizarmos o clock de 25MHz, vamos utilizar a linguagem VHDL, já adiantando que todos os arquivos estão disponíveis para download ao final deste artigo. No Box 1 apresentamos a primeira parte da referida descrição. O código está totalmente comentado para facilitar a compreensão do leitor, porém vamos explica-lo linha a linha, a seguir.

Iniciamos a descrição em VHDL inserindo a biblioteca IEEE (linha 18), do Instituto de Engenheiros Eletricistas e Eletrônicos. Na linha 19 definimos o uso do pacote completo do padrão IEEE 1164. Este pacote contém definições de tipos caracterizados por um estado lógico, que pode ser determinado pelas condições lógicas e de força, que falaremos com maior profundida em artigos futuros, se for do interesse do leitor. Para o presente projeto, basicamente estamos viabilizando o uso de entradas e saídas do tipo “standard logic”.

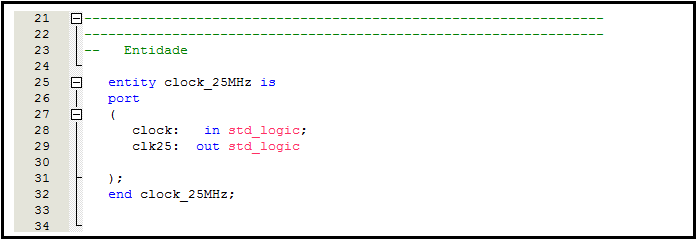

A linguagem VHDL prevê a declaração de uma entidade, que consiste no nível mais alto de abstração do projeto, onde nossas entradas e saídas são declaradas. Para o presente projeto, vamos precisar de uma entrada para o clock principal (o kit que utilizaremos apresenta um cristal onboard que fornece 50MHz ao pino 23 do FPGA) e uma saída para o nosso clock de 25MHz. No Box 2, podemos observar a declaração da entidade.

Na linha 25, com a palavra reservada “entity” declaramos nossa entidade de nome “clock_25MHz”, este nome deve ser idêntico ao nome dado para o seu projeto no Quartus II, software da fabricante Altera. Na linha 26 definimos em “port” nossas entradas e saídas, conforme visto, teremos uma entrada “clock” (linha 28) e uma saída “clk25” (linha 29) ambas declaradas do tipo “std_logic”. As definições in e out são para declaração de entradas e saídas respectivamente. Encerramos a declaração da entidade na linha 32.

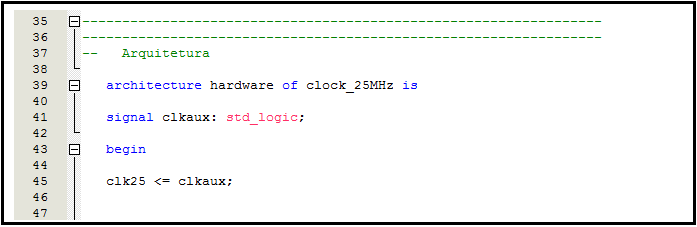

A arquitetura em código VHDL descreve o comportamento do circuito propriamente dito e diferentemente de uma linguagem de programação convencional, as linhas após o “begin” ocorrem de forma concorrente, como se fosse um hardware real! Confira esse trecho do código presente no Box 3.

Você pode dar o nome que quiser para a arquitetura do projeto, por padrão, costumo utilizar sempre o nome “hardware”. Na linha 39, com a palavra “architecture” declaramos a arquitetura de nome “hardware” referenciada à nossa entidade “clock_25MHz”. Na linha 41 declaramos um sinal chamado “clkaux” do tipo std_logic. Neste caso o sinal será utilizado como estado lógico interno do projeto, para podermos gerar o clock desejado. Observe que após o “begin” na linha 43, todo o código é concorrente (ocorre de forma simultânea). Porém, neste código em específico, temos uma única linha nesta região, a linha 45. Nela simplesmente atribuímos o valor do sinal interno clkaux para a nossa saída clk25. A linguagem VHDL é considerada de alto nível e apresenta uma infinidade de recursos, entre eles, a possibilidade de descrevermos código sequencial dentro da arquitetura, para auxiliar na dinâmica de execução do nosso projeto. Esta foi a ideia apresentada no Box 4, onde realizamos a divisão do clock de 50MHz por 2, para obter os 25MHz. Isso foi possível com a utilização de um processo VHDL.

Iniciamos o processo definindo um nome para o mesmo “pro1”, essa questão é opcional do usuário. A palavra reservada “process” abre o processo para que ocorra em lógica sequencial (estas linhas podem ser analisadas como uma linguagem de programação convencional) e observe ainda na linha 52 a palavra “clock” entre parênteses após o “process”. Isso significa que o processo será sensível ao clock externo de 50MHz. Na linha 55 executamos um teste condicional com “if”. Se ocorrer um evento de mudança de estado no clock e o mesmo for igual a 1, a condição será verdadeira e executa o que está após o “then”. Em outras palavras, estamos detectando uma borda de subida em nosso clock de 50MHz. Na linha 59 encerramos o bloco condicional. Portanto, na subida de clock teremos a inversão de nosso sinal interno auxiliar, observe na linha 57, que atribuímos ao sinal a negação dele próprio “clkaux<=not clkaux;”. Na linha 62 encerramos o processo e na linha 65 encerramos a arquitetura.

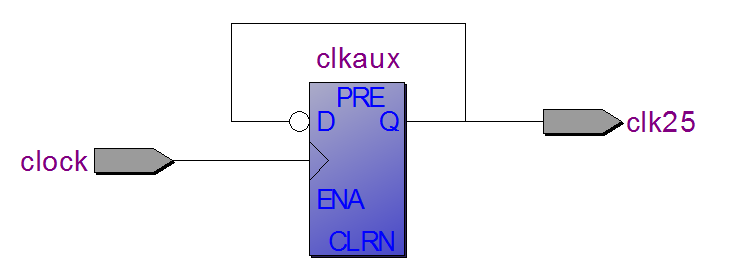

O circuito real se comportará como um divisor de clock por 2, que em hardware é definido através de um flip-flop do tipo D (Figura 2).

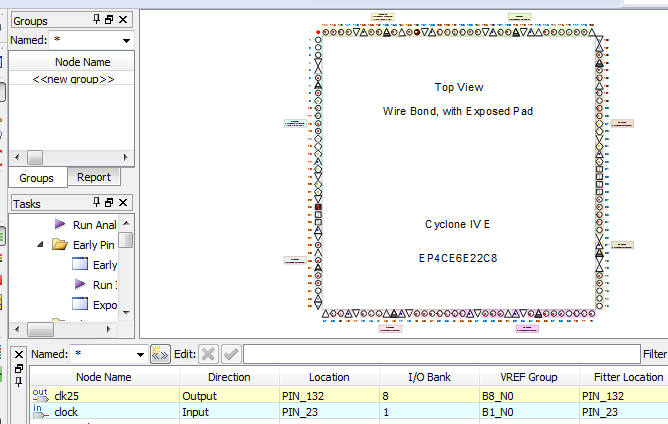

De fato, consiste em um flip-flop sensível ao clock de 50MHz. O sinal em clk25 será metade do clock de entrada, pois a saída Q trocará o estado a cada borda de subida. Também observe que o sinal clkaux atua como controle de dados. Em resumo, temos um processo sensível ao clock, que a cada borda de subida inverte o estado do sinal clkaux e este é atribuído à saída clk25 que está indexada ao pino 132 do FPGA Cyclone IV. Esta definição também é realizada no próprio QuartusII, veja na Figura 3, o pino de clock associado ao pino 23 do FPGA e o pino de saída clk25 associado ao pino 132, que foi escolhido para o projeto.

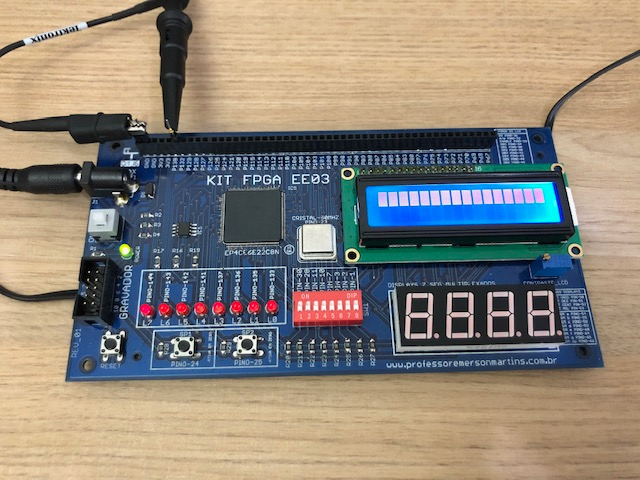

Na Figura 4 apresentamos o kit utilizado para o teste prático desta descrição, que contém o Cyclone IV e mais alguns recursos adicionais.

Confira na Figura 4 a forma de onda de 25MHz medida no osciloscópio.

Para os interessados em se aprofundar no tema FPGA, que é algo muito promissor e sem dúvida será um diferencial de todo profissional de eletrônica, temos disponível em nossa loja a apostila sobre FPGAs, que pode ser adquirida aqui: https://wrkits.com.br/catalog/show/157

Quem desejar aprender a linguagem VHDL e se tornar profissional na mesma, o livro sugerido é o VHDL Descrição e Síntese de Circuitos Digitais do autor Roberto d’Amore, que pode ser encontrado aqui: https://amzn.to/2LV5T3m

Em nosso canal WR Kits no YouTube, também temos um curso completo e gratuito sobre VHDL e FPGAs, que contém 80 vídeo aulas com muitos exemplos práticos e pode ser conferido aqui: https://www.youtube.com/playlist?list=PLZ8dBTV2_5HS79fVexGTtCMDUp7kjnumS

Adicionalmente no presente artigo temos um vídeo demonstrando o funcionamento do código descrito em VHDL no kit EE03 e também disponibilizamos os arquivos do QuartusII para você fazer o download.