O que é arquitetura RISC e CISC e suas diferenças

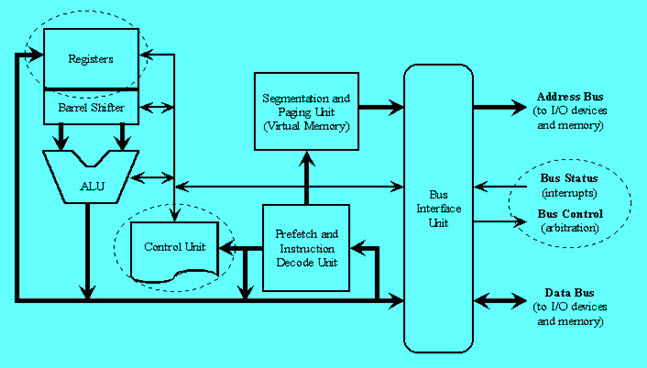

A arquitetura da Unidade Central de Processamento (CPU) opera a capacidade de funcionar desde a “Arquitetura do Conjunto de Instruções” até onde foi projetada. O projeto arquitetônico da CPU é Computação do conjunto de instruções reduzido (RISC) e Computação do conjunto de instruções complexo (CISC). O CISC tem a capacidade de executar operações em várias etapas ou modos de endereçamento dentro de um conjunto de instruções. É o design da CPU onde uma instrução funciona em vários atos de baixo nível. Por exemplo, armazenamento de memória, carregamento da memória e uma operação aritmética.

A computação do conjunto reduzido de instruções é uma estratégia de projeto da Unidade Central de Processamento baseada na visão de que um conjunto básico de instruções oferece ótimo desempenho quando combinado com uma arquitetura de microprocessador. Essa arquitetura tem a capacidade de executar as instruções usando alguns ciclos de microprocessador por instrução. Este artigo discute a arquitetura RISC e CISC com diagramas apropriados. A parte de hardware da Intel é chamada de Complex Instruction Set Computer (CISC), e o hardware da Apple é Reduced Instruction Set Computer (RISC).

Conteudo

O que são Arquiteturas RISC e CISC?

Um computador com conjunto de instruções complexo é um computador onde instruções únicas podem executar várias operações de baixo nível, como uma carga da memória, uma operação aritmética e um armazenamento de memória, ou são realizadas por processos de várias etapas ou modos de endereçamento em instruções únicas, como seu nome propõe “Conjunto de Instruções Complexas”.

Um computador com conjunto reduzido de instruções é um computador que usa apenas comandos simples que podem ser divididos em várias instruções que atingem a operação de baixo nível dentro de um único ciclo CLK, como o próprio nome propõe “Conjunto de instruções reduzido”

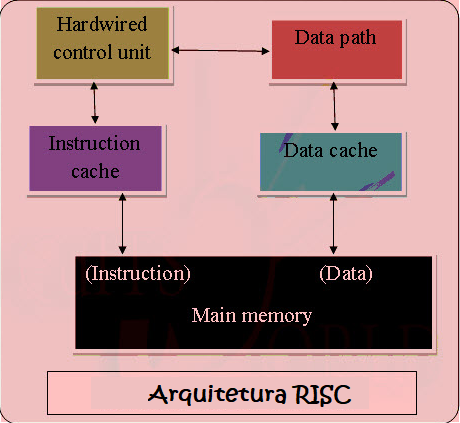

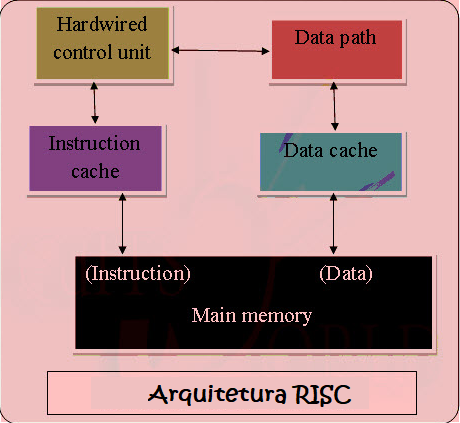

Arquitetura RISC

O termo RISC significa ”Computador com Conjunto de Instruções Reduzido”. É um plano de design de CPU baseado em pedidos simples e atua rápido.

Este é um conjunto pequeno ou reduzido de instruções. Aqui, espera-se que cada instrução atinja trabalhos muito pequenos. Nesta máquina, os conjuntos de instruções são modestos e simples, o que auxilia na composição de comandos mais complexos. Cada instrução tem aproximadamente um comprimento similar; estes são enrolados juntos para realizar tarefas compostas em uma única operação. A maioria dos comandos é concluída em um ciclo de máquina. Este pipelining é uma técnica crucial usada para acelerar as máquinas RISC.

Conjunto de instruções reduzido O computador é um microprocessador projetado para executar poucas instruções ao mesmo tempo. Com base em pequenos comandos, esses chips precisam de menos transistores, o que torna os transistores baratos para projetar e produzir. Os recursos do RISC incluem o seguinte.

- A demanda por decodificação é menor

- Poucos tipos de dados em hardware

- Registro de uso geral Idêntico

- Conjunto de instruções uniforme

- Nós de endereçamento simples

Além disso, ao escrever um programa, o RISC facilita, permitindo que o programador de computador elimine códigos desnecessários e para de desperdiçar ciclos.

Características

As características da arquitetura RISC incluem o seguinte.

- As instruções simples são usadas na arquitetura RISC.

- O RISC ajuda e suporta alguns tipos de dados simples e sintetiza tipos de dados complexos.

- O RISC utiliza modos de endereçamento simples e instruções de comprimento fixo para pipelining.

- O RISC permite que qualquer registro seja usado em qualquer contexto.

- Tempo de execução de um ciclo

- A quantidade de trabalho que um computador pode realizar é reduzida separando as instruções “LOAD” e “STORE”.

- O RISC contém um grande número de registradores para evitar várias interações com a memória.

- No RISC, o Pipelining é fácil, pois a execução de todas as instruções será feita em um intervalo de tempo uniforme, ou seja, um clique.

- No RISC, mais RAM é necessária para armazenar instruções em nível de montagem.

- Instruções reduzidas precisam de um número menor de transistores no RISC.

- RISC usa o modelo de memória Harvard significa que é Harvard Architecture.

- Um compilador é usado para realizar a operação de conversão significa converter uma instrução de linguagem de alto nível no código de seu formulário.

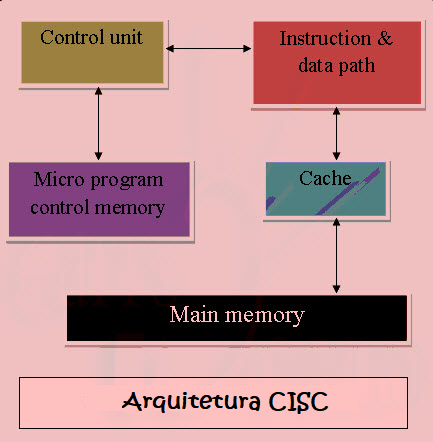

Arquitetura CISC

O termo CISC significa ”Complex Instruction Set Computer”. É um plano de design de CPU baseado em comandos únicos, que são qualificados na execução de operações em várias etapas.

Os computadores CISC têm pequenos programas. Possui um grande número de instruções compostas, que levam muito tempo para serem executadas. Aqui, um único conjunto de instruções é protegido em várias etapas; cada conjunto de instruções tem mais de 300 instruções separadas. As instruções máximas são concluídas em dois a dez ciclos de máquina. No CISC, o pipeline de instruções não é facilmente implementado.

As máquinas CISC têm boas atuações, baseadas na visão geral dos compiladores de programas; uma vez que a gama de instruções inovadoras podem ser obtidas simplesmente em um conjunto de instruções. Eles projetam instruções compostas em um único e simples conjunto de instruções.

Eles alcançam processos de baixo nível, o que torna mais fácil ter grandes nós de endereçamento e tipos de dados adicionais no hardware de uma máquina. Mas o CISC é considerado menos eficiente que o RISC, devido à sua incompetência em eliminar códigos que levam ao desperdício de ciclos. Além disso, os chips de microprocessador são difíceis de entender e programar, devido à complexidade do hardware.

- A Arquitetura do Conjunto de Instruções é um meio para permitir a comunicação entre o programador e o hardware. Parte de execução de dados, cópia de dados, exclusão ou edição são os comandos do usuário usados no microprocessador e, com este microprocessador, a arquitetura do conjunto de instruções é operada.

- As principais palavras-chave usadas na Arquitetura do Conjunto de Instruções acima são as seguintes

Conjunto de Instruções: Conjunto de instruções dadas para executar o programa e direcionam o computador manipulando os dados. As instruções estão no formato – Opcode (código operacional) e Operando. Onde, o opcode é a instrução aplicada para carregar e armazenar dados, etc. O operando é um registrador de memória onde a instrução é aplicada.

Modos de endereçamento: Os modos de endereçamento são como os dados são acessados. Dependendo do tipo de instrução aplicada, os modos de endereçamento são de vários tipos, como um modo direto onde os dados diretos são acessados ou o modo indireto onde a localização dos dados é acessada. Processadores com ISA idêntico podem ser muito diferentes na organização. Processadores com ISA idêntico e organização quase idêntica ainda não são quase idênticos.

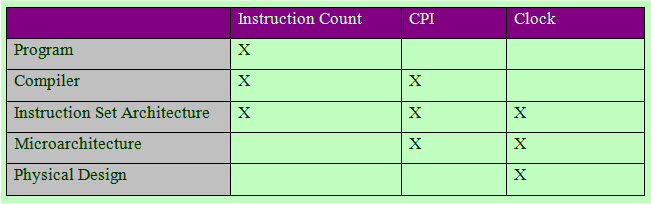

O desempenho da CPU é dado pela lei fundamental

![]()

Assim, o desempenho da CPU depende da Contagem de Instrução, CPI (Ciclos por Instrução) e tempo de ciclo do Relógio. E todos os três são afetados pela arquitetura do conjunto de instruções.

Isso sublinha a importância da arquitetura do conjunto de instruções. Existem duas arquiteturas de conjuntos de instruções predominantes

Exemplos de processadores CISC

IBM 370/168 – Foi introduzido no ano de 1970. O projeto CISC é um processador de 32 bits e quatro registradores de ponto flutuante de 64 bits.

VAX 11/780 – O design do CISC é um processador de 32 bits e suporta vários modos de endereçamento e instruções de máquina da Digital Equipment Corporation.

Intel 80486 – Foi lançado no ano de 1989 e é um processador CISC, que possui instruções de comprimento variando de 1 a 11 e terá 235 instruções.

Características

As características da arquitetura CISC incluem o seguinte.

- A lógica de decodificação de instruções será Complexa.

- Uma instrução é necessária para suportar vários modos de endereçamento.

- Menos espaço no chip é suficiente para registradores de uso geral para as instruções que 0 são operadas diretamente na memória.

- Vários projetos CISC são configurados com dois registradores especiais para o ponteiro de pilha, tratamento de interrupções, etc.

- MUL é referido como uma “instrução complexa

Comparação entre RISC e CISC

RISC significa ‘Computador de Conjunto de Instruções Reduzidas, enquanto CISC significa Computador de Conjunto de Instruções Complexas. Os processadores RISC possuem um conjunto menor de instruções com poucos nós de endereçamento. Os processadores CISC possuem um conjunto maior de instruções com muitos nós de endereçamento.

Unidade de memória

O RISC não possui unidade de memória e usa hardware separado para implementar instruções. CISC tem uma unidade de memória para implementar instruções complexas

Programa

RISC tem uma unidade de programação hard-wired. O CISC tem uma unidade de microprogramação

Projeto

RISC é um projeto de compilador complexo. CISC é um projeto de compilador fácil

Cálculos

Os cálculos RISC são mais rápidos e precisos. Os cálculos do CISC são lentos e precisos

Decodificação

A decodificação RISC de instruções é simples. A decodificação de instruções CISC é complexa

Tempo

O tempo de execução é muito menor no RISC. O tempo de execução é muito alto no CISC.

Memória externa

O RISC não requer memória externa para cálculos. O CISC requer memória externa para cálculos.

Tubulação

O RISC Pipelining funciona corretamente. O Pipelining CISC não funciona corretamente.

Parando

A paralisação do RISC é principalmente reduzida em processadores. Os processadores CISC geralmente param.

Expansão de código

A expansão do código pode ser um problema no RISC, enquanto no CISC a expansão do código não é um problema.

Espaço em disco

O espaço é economizado no RISC, enquanto no CISC o espaço é desperdiçado. Os melhores exemplos de arquitetura de conjunto de instruções CISC incluem VAX, PDP-11, Motorola 68k e seus PCs desktop na arquitetura x86 da Intel, enquanto os melhores exemplos de arquitetura RISC incluem DEC Alpha, ARC, AMD 29k, Atmel AVR, Intel i860, Blackfin , i960, Motorola 88000, MIPS, PA-RISC, Power, SPARC, SuperH e ARM também.

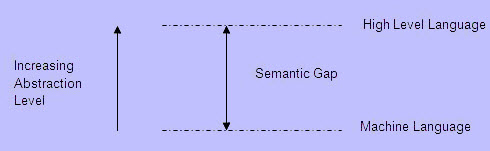

LACUNA SEMÂNTICA

Ambas as arquiteturas RISC e CISC foram desenvolvidas como uma tentativa de cobrir a lacuna semântica.

Para melhorar a eficiência do desenvolvimento de software, surgiram várias linguagens de programação poderosas , como Ada, C, C++, Java, etc. Elas fornecem um alto nível de abstração, concisão e poder. Por essa evolução, a lacuna semântica cresce. Para permitir a compilação eficiente de programas de linguagem de alto nível, os designs CISC e RISC são as duas opções.

Os projetos CISC envolvem arquiteturas muito complexas, incluindo um grande número de instruções e modos de endereçamento, enquanto os projetos RISC envolvem um conjunto de instruções simplificado e o adaptam aos requisitos reais dos programas do usuário.

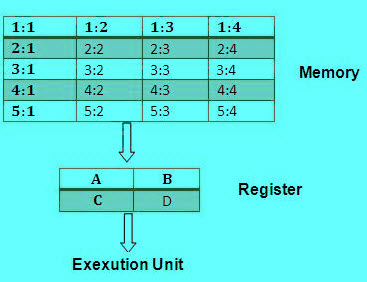

Multiplicação de dois números na memória

Se a memória principal for dividida em áreas numeradas da linha 1:coluna 1 à linha 5: coluna 4. Os dados são carregados em um dos quatro registros (A, B, C ou D). Para encontrar a multiplicação de dois números – Um armazenado no local 1:3 e outro armazenado no local 4:2 e armazenar de volta o resultado em 1:3.

Aplicações de RISC e CISC

O RISC é usado em aplicativos de ponta, como processamento de vídeo, telecomunicações e processamento de imagens. O CISC é usado em aplicações de baixo custo, como sistemas de segurança, automação residencial, etc.

Vantagens e desvantagens

As vantagens da arquitetura RISC incluem o seguinte.

- A arquitetura RISC ( computação com conjunto de instruções reduzido ) possui um conjunto de instruções, para que os compiladores de linguagem de alto nível possam produzir código mais eficiente

- Permite liberdade de uso do espaço nos microprocessadores devido à sua simplicidade.

- Muitos processadores RISC usam os registradores para passar argumentos e manter as variáveis locais.

- As funções RISC usam apenas alguns parâmetros e os processadores RISC não podem usar as instruções de chamada e, portanto, usam uma instrução de comprimento fixo que é fácil de pipeline.

- A velocidade da operação pode ser maximizada e o tempo de execução pode ser minimizado.

Um número muito menor de formatos instrucionais, alguns números de instruções e alguns modos de endereçamento são necessários.

As desvantagens da arquitetura RISC incluem o seguinte.

- Principalmente, o desempenho dos processadores RISC depende do programador ou compilador, pois o conhecimento do compilador desempenha um papel vital ao alterar o código CISC para um código RISC

- Ao reorganizar o código CISC para um código RISC, denominado como expansão de código, o tamanho aumentará. E, a qualidade dessa expansão de código dependerá novamente do compilador e também do conjunto de instruções da máquina.

- O cache de primeiro nível dos processadores RISC também é uma desvantagem do RISC, no qual esses processadores possuem grandes caches de memória no próprio chip. Para alimentar as instruções, eles exigem sistemas de memória muito rápidos.

As vantagens da arquitetura CISC incluem o seguinte.

- A microprogramação é uma linguagem assembly fácil de implementar e menos dispendiosa do que a fiação de uma unidade de controle.

- A facilidade de microcodificação de novas instruções permitiu que os projetistas tornassem as máquinas CISC compatíveis de forma ascendente:

- À medida que cada instrução se tornava mais completa, menos instruções podiam ser usadas para implementar uma determinada tarefa.

As desvantagens da arquitetura CISC incluem o seguinte.

- O desempenho da máquina fica mais lento devido à quantidade de tempo de clock usada por diferentes instruções.

- Apenas 20% das instruções existentes são usadas em um evento típico de programação, embora existam várias instruções especializadas na realidade que nem são usadas com frequência.

- Os códigos condicionais são definidos pelas instruções CISC como um efeito colateral de cada instrução que leva tempo para essa configuração – e, à medida que a instrução subsequente altera os bits do código de condição -, o compilador precisa examinar os bits do código de condição antes que isso aconteça.

Da comparação acima de RISC e CISC, finalmente, podemos concluir que não podemos distinguir entre tecnologia RISC e CISC porque ambas são aptas em sua aplicação precisa. Hoje, os designers RISC e CISC estão fazendo tudo para obter uma vantagem sobre a concorrência. Esperamos que você tenha entendido melhor esse conceito. Além disso, qualquer dúvida em relação a este conceito, ou para implementar quaisquer projetos elétricos e eletrônicos, por favor, dê seu feedback comentando na seção de comentários abaixo. Aqui está uma pergunta para você, quais são as diferentes arquiteturas disponíveis?