Como são produzidos os circuitos integrados?

Conteudo

Resumo

A fabricação de wafer e chip são duas etapas para fazer circuitos integrados. A fabricação de wafer inclui duas etapas principais, fabricação de lingotes e fabricação de wafer. Ele pode ser subdividido nos seguintes processos principais: polissilício-monocristalino de silício-lingote de crescimento-lingote corte e inspeção-moagem de diâmetro externo —— Corte — Borda redonda — Retificação de superfície — Gravura — Remoção de defeitos — Polimento— (Epitaxial — Gravação — Defeito remoção) —Limpeza — Inspeção — Embalagem. A fabricação do chip pode ser dividida em várias etapas: Fabricação de Wafer, Sonda de Wafer, Embalagem, Teste Inicial e Teste Final e outras etapas.

I. Introdução

Um circuito integrado é um dispositivo ou componente eletrônico em miniatura com funções de circuito específicas. Os componentes necessários em um circuito, como transistores, resistores, capacitores e indutores, são interconectados com a fiação para fazer um ou vários pequenos wafers semicondutores ou substratos dielétricos e, em seguida, encapsulados em um tubo e concha. Todos os componentes foram integrados em uma estrutura, tornando os componentes eletrônicos um grande passo em direção à miniaturização, baixo consumo de energia, inteligência e alta confiabilidade. É representado no circuito pela letra “IC”. Os inventores dos circuitos integrados foram Jack Kilby (circuitos integrados baseados em germânio (Ge)) e Robert Neuss (circuitos integrados baseados em silício (Si)). A maioria das aplicações na indústria de semicondutores hoje são circuitos integrados baseados em silício.

O circuito integrado é um tipo de dispositivo semicondutor desenvolvido no final dos anos 1950 e 1960. É feito por meio de processos de fabricação de semicondutores, como oxidação, fotolitografia, difusão, epitaxia e evaporação de alumínio. Ele integra o semicondutor, resistor, capacitor e outros componentes em um pequeno pedaço de silício para formar um circuito com certas funções e, em seguida, é embalado em um tubo e concha. O invólucro da embalagem tem uma variedade de formas, como invólucro redondo, plano ou duplo em linha. A tecnologia de circuito integrado inclui tecnologia de fabricação de chips e tecnologia de design, que se refletem principalmente em equipamentos de processamento, tecnologia de processamento, teste de embalagem, produção em massa e recursos de inovação de design.

II Processo de Fabricação de Circuito Integrado

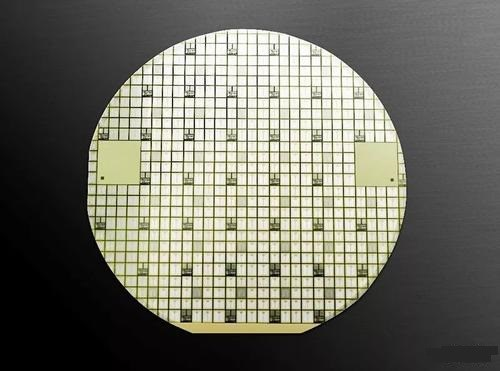

1. Fabricação de wafer (cristal crescimento-corte-borda moagem-polimento-embalagem-transporte)

Crescimento de Cristal

O crescimento do cristal requer um sistema de extração de cristal automatizado de alta precisão. O minério de quartzo é refinado em forno elétrico a arco, clorado com ácido clorídrico e destilado para fazer polissilício de alta pureza, cuja pureza chega a 0,99999999999. Uma pequena quantidade de “dopantes” eletroativos, como arsênio, boro, fósforo ou antimônio, é adicionada ao polissilício obtido pelo refino do minério de quartzo e eles são fundidos em um forno de alta temperatura. Um longo cabo de cristal é então usado como cristal semente e inserido na parte inferior do polissilício fundido. Em seguida, gire o cabo e puxe-o lentamente para fora. Após o resfriamento, forma-se um lingote cilíndrico de silício monocristalino, ou seja, uma haste de silício. Esse processo é chamado de “crescimento de cristal”. As hastes de silício têm geralmente 3 pés de comprimento e vêm em diâmetros de 6, 8 e 12 polegadas. Depois que o lingote de silício é moído, polido e fatiado, ele se torna a matéria-prima básica para a fabricação de circuitos integrados-wafers.

Corte / Desbaste de Borda / Polimento de Superfície

O fatiamento usa lâminas internas especiais para cortar barras de silício em placas finas com geometrias precisas. Em seguida, a superfície e as bordas do wafer são polidas, polidas e limpas. As arestas afiadas do wafer recém-cortado são arredondadas para remover arranhões e impurezas, e um wafer de silício quase perfeito é obtido.

Acondicionamento / envio

Após a conclusão da fabricação do wafer, é necessário equipamento profissional para embalar e transportar esses wafers de silício quase perfeitos. As operadoras de wafer fornecem aos fabricantes de semicondutores uma seleção e colocação de wafer rápida, consistente e confiável.

2. Deposição

Deposição epitaxial

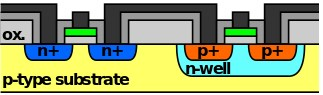

A camada epitaxial é a primeira camada depositada em uma pastilha semicondutora. A maioria das deposições de crescimento epitaxial modernas usa deposição de vapor químico de baixa pressão (LPCVD) para fazer crescer filmes de silício em substratos de silício. A camada epitaxial é formada de silício ultra-puro e atua como uma camada tampão para evitar que impurezas prejudiciais entrem no substrato de silício. No passado, os processos bipolares geralmente exigiam o uso de camadas epitaxiais e a tecnologia CMOS não era usada. Uma vez que a camada epitaxial pode permitir o uso de wafers com um pequeno número de defeitos, ela pode ser mais usada em wafers de 300 mm no futuro.

Deposição de vapor químico

A deposição de vapor químico (CVD) é uma técnica que deposita uma mistura na superfície do wafer ao decompor moléculas de gás. O CVD produz muitos intermediários térmicos não plasmáticos. Um aspecto comum é que esses intermediários ou precursores são todos gases. Existem muitos tipos de tecnologias CVD, como CVD térmico, CVD de plasma, CVD não plasma, CVD atmosférico, LPCVD, HDPCVD, LDPCVD, PECVD, etc., que são aplicados a diferentes aspectos da fabricação de semicondutores.

Deposição física de vapor

O material de interconexão de metal mais comum em um wafer é o Al, e um método de deposição física de vapor (PVD) é comumente usado para preparar filmes de material metálico. No sistema PVD, o alvo de Al é bombardeado com íons, de modo que os átomos de Al na superfície do alvo escapam com uma certa energia e, em seguida, são depositados na superfície do wafer. O PVD também é usado para depositar camadas de barreira e sementes, bem como filmes de cobre para interconexões duplas embutidas.

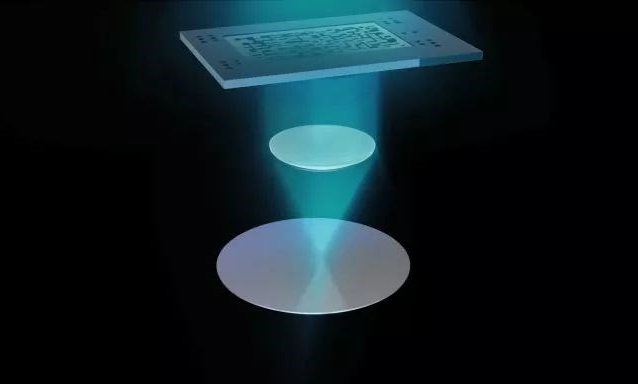

3. Fotolitografia

Fotolitografia é o processo de impressão de padrões de circuitos de chips em wafers. É a etapa mais crítica na fabricação de circuitos integrados. É responsável por cerca de 35% do custo geral de fabricação em todo o processo de fabricação de chips. A litografia também é um fator importante que determina o desenvolvimento de circuitos integrados de acordo com a Lei de Moore. Sem o avanço da tecnologia de litografia, os circuitos integrados não serão capazes de passar de micrômetros para submícrons profundos e, em seguida, entrar na era do nanômetro.

O processo de fotolitografia transfere o padrão de máscara para o fotorresiste na superfície do wafer. Primeiro, o equipamento de processamento de fotorresiste reveste o fotorresiste na superfície do wafer e, em seguida, repete o processo de exposição e revelação passo a passo para formar os gráficos necessários no wafer. A dificuldade de um processo é geralmente expressa pelo número de máscaras que um processo precisa passar. De acordo com diferentes métodos de exposição, a litografia pode ser dividida em tipo de contato, tipo de proximidade e tipo de projeção; De acordo com o número de planos litográficos, há litografia de alinhamento unilateral e litografia de alinhamento dupla face; Dependendo do tipo de fotoresiste, existem fotoresiste fino e fotorresiste espesso. O processo de litografia geral inclui pré-processamento, nivelamento, pré-cozimento, exposição de alinhamento, desenvolvimento e pós-cozimento. As operações no processo podem ser ajustadas de acordo com a situação real.

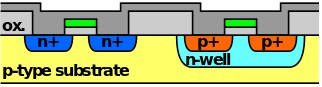

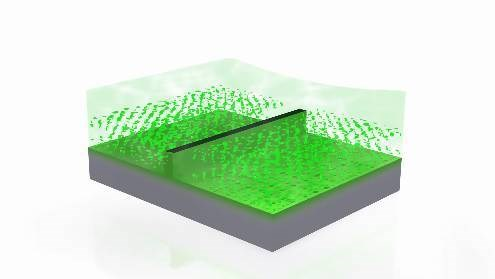

4. Gravura

No processo de fabricação do circuito integrado, após o registro, a exposição e o desenvolvimento da máscara, o padrão necessário é copiado no filme resistente ou o feixe de elétrons é desenhado diretamente para gerar o padrão no filme resistente. Este padrão é então transferido com precisão para o filme dielétrico (como óxido de silício, nitreto de silício, polissilício) ou filme de metal sob a máscara para produzir o padrão de camada fina desejado. A gravação consiste em usar métodos químicos, físicos ou químicos e físicos para remover seletivamente a parte da camada de película fina que não é mascarada pela resistência, de modo a obter um padrão na película fina que seja completamente consistente com a resistência filme. A gravação de plasma é a ionização de gás reativo para formar um plasma sob condições específicas. O plasma remove seletivamente as substâncias da bolacha, e as substâncias restantes formam um padrão de chip na bolacha.

5. Implantação de íons

O substrato do wafer é um material de silício puro, que é não condutor ou fracamente condutor. Para ter condutividade no chip, um pequeno número de impurezas deve ser adicionado ao wafer, geralmente arsênico, boro e fósforo. A dopagem pode ser feita em forno de difusão ou por implantação iônica. Algumas aplicações avançadas são dopadas com implantação iônica. Existem três tipos de implantação de íons: implantação de íons de corrente média, implantação de íons de alta corrente / baixa energia e implantação de íons de alta energia, que são adequados para diferentes necessidades de aplicação.

6. Processamento Térmico

O processamento térmico é o uso de energia térmica para eliminar algumas das tensões internas no objeto. A energia aplicada aumentará a vibração e a difusão dos átomos da rede e defeitos no objeto, de modo que o arranjo dos átomos pode ser reorganizado. O processamento térmico é um processo após o processo de fabricação por deposição para alterar as propriedades mecânicas do filme depositado.

No momento, existem duas aplicações principais da tecnologia de tratamento térmico: uma usa isoladores ultra-low-k para aumentar a dureza de filmes porosos, a outra usa nitretos de alta resistência para aumentar a tenacidade e resistência à tração do filme depositado para melhorar o dispositivo atuação. No reator de tratamento térmico de UV, o filme fino de deposição de vapor químico aprimorado por plasma altera as propriedades do filme por meio de uma combinação de luz e calor. O processo de tratamento térmico ultravioleta no filme de nitreto de alta resistência faz com que as conexões sejam reorganizadas e o contato espacial seja melhor, resultando no alto nível de resistência necessário para melhorar o desempenho do dispositivo.

7. Polimento químico-mecânico (CMP)

Uma das chaves para o avanço da tecnologia de chip é o aumento no número de camadas por chip, o número crescente de camadas empilhadas em um chip e a irregularidade de cada camada aumentará a dificuldade das imagens litográficas de circuito fino. O sistema CMP usa uma almofada de polimento e um abrasivo químico para polir e nivelar seletivamente a camada depositada. CMP inclui planarização dielétrica de polissilício metálico (PMD), planarização de filme de isolamento intercamada (ILD) e planarização de tungstênio. CMP é uma tecnologia chave na tecnologia de interconexão de cobre damasceno.

8. Metrologia Wafer

No processo de fabricação do chip, para garantir que o wafer seja processado de acordo com os requisitos de design predeterminados, um grande número de inspeções e medições devem ser confirmadas, incluindo a medição da largura da linha no chip, a medição da espessura de cada camada , a medição da topografia da superfície de cada camada e a medição de cada camada. Algumas medidas eletrônicas de desempenho.

Com o desenvolvimento contínuo de processos de semicondutores e tecnologias de fabricação, esses testes se tornaram uma parte indispensável para melhorar a produção em massa e o rendimento. No processo de interconexão de cobre, devido ao uso de tecnologia de largura de linha mais fina e materiais dielétricos de baixo k, equipamentos de teste mais sofisticados e novos métodos de teste precisam ser desenvolvidos.

A inspeção inclui principalmente três tipos: inspeção óptica, inspeção de película fina e inspeção eletrônica de varredura de dimensão crítica (CD-SEM). Uma importante tendência de desenvolvimento da inspeção de wafer é a integração de vários métodos de medição em um equipamento de processo.

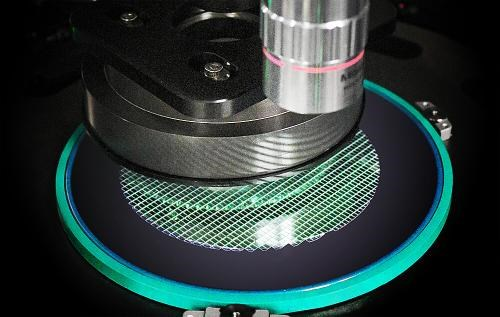

9. Inspeção de Wafer (Partículas)

Muitas etapas no processo de fabricação de wafer requerem inspeção de contaminação de wafer, como inspeção de wafer nua, monitoramento de equipamento (usando equipamento de processo para controlar o tamanho de partícula depositado no wafer) e inspeção após CMP, CVD e implantação de íons. Normalmente, essas inspeções são feitas antes da aplicação do wafer ou antes que a camada fotorresistente seja exposta, o que é conhecido como inspeção sem padrão.

10. Teste de Sonda Wafer

O teste da sonda do wafer é um teste de pino de cada molde no wafer fabricado. Durante o teste, o wafer é fixado em um mandril de sucção a vácuo. Sondas semelhantes a cabelos estão em contato com cada junta de solda no chip. Durante o processo de teste, o desempenho elétrico e a função do circuito de cada chip são detectados. Os grãos não qualificados serão marcados e, então, quando o chip for cortado em partículas de chip independentes, as partículas de chip não qualificadas marcadas serão eliminadas. Os dados relevantes da detecção da sonda agora podem ser usados para ajudar a melhorar o rendimento na fabricação de wafer.

11. Embalagem (Montagem e Embalagem)

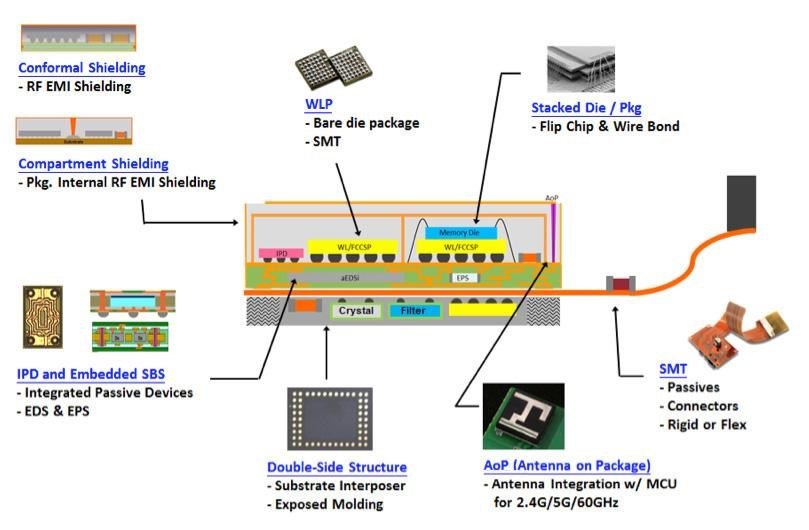

A tecnologia de empacotamento se desenvolveu muito rápido nos últimos anos, principalmente porque (a) A complexidade do chip está cada vez mais alta: o número de transistores contidos no chip aumentou drasticamente e os pinos também aumentaram. Novas tecnologias de embalagem são necessárias para atender a essas necessidades. (b) Miniaturização de produtos eletrônicos: os produtos eletrônicos de hoje requerem tamanho pequeno, funções poderosas e baixo consumo de energia, o que também significa requisitos mais elevados para ligação de fios, e a forma de embalagem deve se adaptar a essas mudanças.

Os chips no wafer são cortados em chips individuais e então embalados de forma que os chips possam ser colocados no PCB. O equipamento necessário aqui inclui máquinas de corte de bolachas, máquinas de fixação de matrizes (empacotar chips em estruturas de chumbo), conectores de fios (responsáveis por conectar chips e estruturas de chumbo, como soldagem de fios de ouro e soldagem de fios de cobre). Diferentes tipos de fios são usados no processo de ligação dos fios: ouro (Au), alumínio (Al), cobre (Cu). Cada material tem suas vantagens e desvantagens e é colado por métodos diferentes. Com o surgimento de embalagens multicamadas e até aplicações de embalagens 3D, a demanda por wafers ultrafinos também está aumentando.

12. Teste Final

Como o rendimento final do chip não pode chegar a 100%, a inspeção do chip torna-se mais importante. Como detectar chips de alto desempenho e como detectá-los rapidamente são muito importantes. Considerando que cada chip precisa ser inspecionado, a fábrica deve equilibrar os custos em toda a linha. Isso levou à nova geração de equipamentos de teste com funções de inspeção mais poderosas, custos mais baixos e velocidades de inspeção mais rápidas.